# CW001007 ARM7TDMI Microprocessor Core

Datasheet

The LSI Logic CW001007 core is an implementation of the Advanced RISC Machines ARM7TDMI 32-bit RISC microprocessor developed by Advanced RISC Machines. The CW1007 meets the requirements of the LSI Logic CoreWare<sup>®</sup> methodology and is implemented using LSI Logic G11<sup>™</sup> 0.25-micron process technology. The G11-p 2.5 V core supports speeds up to 80 MHz. The G11-v 1.8 V core supports speeds up to 55 MHz (under worst case commercial conditions) and consumes less than 1 mW per MHz. The core area is just under 2.5 mm<sup>2</sup>. With its high performance, low power requirements, and small size,the ARM7TDMI core is ideal for a wide variety of embedded applications.

The CW001007 core employs an innovative architectural strategy known as *THUMB*, which can execute both 32-bit and 16-bit instructions to support high volume applications with memory restrictions and applications where code density is an issue. Because it employs both the ARM<sup>®</sup> and THUMB instruction sets, it allows a wide choice of development tools and third-party RTOSs (real-time operating systems) created and supported by ARM and a host of third-party vendors. See "THUMB Architecture," on page 7 for more information.

The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, so the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers (CISC). This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective chip.

The ARM memory interface has been designed to allow the performance potential to be realized without incurring high costs in the memory system. Speed critical control signals are pipelined to exploit the fast local access modes offered by industry-standard dynamic RAMs.

## **Features and Benefits**

- LSI Logic 0.25 micron G11 technology

- RTL design approach

- ARM 32-bit RISC execution engine delivers up to 80 MHz

- Extensive set of peripherals designed to the AMBA standard

- Built-in code decompression (THUMB)

- Includes full scan test structures

- Includes ARM ICEBreaker debugger

- A choice of G11-p for high performance applications or G11-v for low power applications

- Access to full CoreWare library

- High density and a small die size increase the area available for integration of other logic

- Simplified process migration

- Simplified CPU customization

- Complete and accurate timing model

- Compatibility with a wide range of parts from other vendors

- Supported by an existing array of ARM development tools and RTOSs

- Simplifies system development

- Facilities design reuse and customization

- Reduces total system memory requirements

- Very high fault coverage for manufacturing test

- Ideal for deeply embedded ASICs

### Description

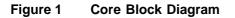

Figure 1 shows a block diagram of the CW001007 core. The CW001007 core consists of four major blocks: ICEBreaker, TAP (Test Access Port ) Controller, Bus Splitter, and the Microprocessor (shown in more detail in Figure 2).

The ICEBreaker module provides integrated debugging support for the Internal Core module. It consists of two real-time watchpoint units, a control register, and a status register. The TAP controller module controls three JTAG scan chains used for testing, debugging, and programming the ICEBreaker. A fourth scan chain is also provided for an external boundary chain around the pads of a packaged device.

The Bus Splitter is used to split the internal bidirectional data bus into three unidirectional buses for ASIC designs that prohibit bidirectional data buses.

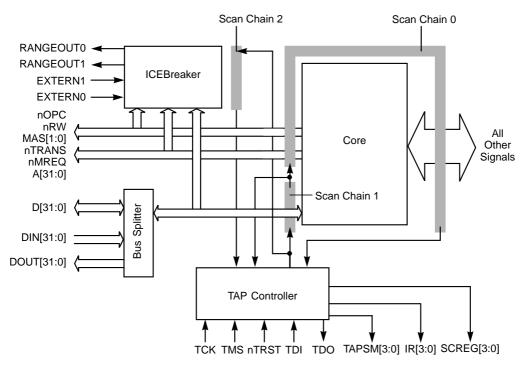

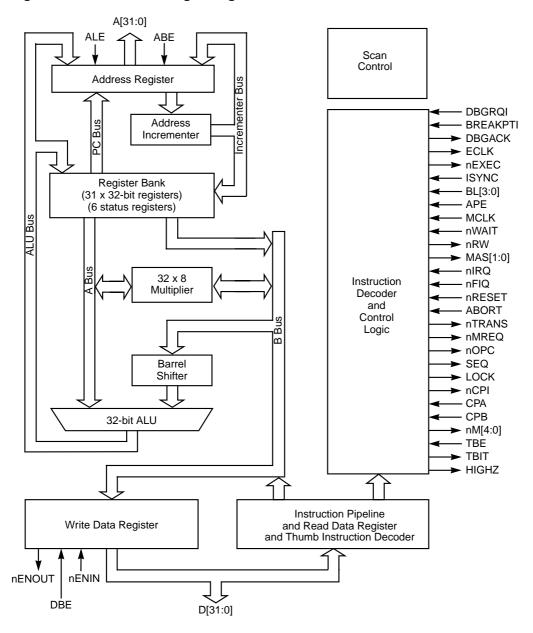

The microprocessor module provides the main functionality of the microprocessor core. Figure 2 shows the microprocessor module in more detail.

#### Figure 2 Microprocessor Module Block Diagram

### Pipelining

A three-stage pipeline is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

#### **Building Blocks**

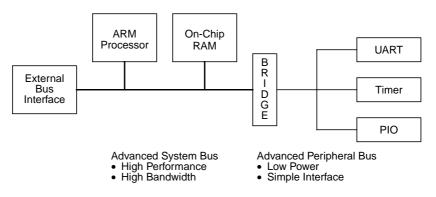

To facilitate system design, LSI Logic offers a complete library of peripherals implemented around the popular AMBA open bus standard. These peripherals can be used as-is, or modified to suit the specific application. Figure 3 shows a typical AMBA system that incorporates the ARM7TDMI core.

#### **Debug and Full Scan**

The ARM7TDMI core uses full scan methodology for high fault coverage and contains the ARM ICEBreaker module for effective debugging, even in the most deeply embedded ASICs. As part of the LSI Logic CoreWare Library, the ARM7TDMI core is supported by LSI Logic ASIC design methodology, tools, and expert technical support.

## **THUMB** Architecture

The CW001007 processor has two instruction sets:

- Standard 32-bit ARM set

- A 16-bit THUMB set

The THUMB set is a super-reduced instruction set. Its 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because THUMB code operates on the same 32-bit register set as ARM code.

THUMB code is able to provide up to 65% of the code size of ARM and 160% of the performance of an equivalent ARM processor connected to a 16-bit memory system.

THUMB instructions operate with the standard ARM register configuration, allowing excellent interoperability between ARM and THUMB states. Each 16-bit THUMB instruction has a corresponding 32-bit ARM instruction with the same effect on the processor model.

The major advantage of a 32-bit (ARM) architecture over a 16-bit architecture is its ability to manipulate 32-bit integers with single instructions and to address a large address space efficiently. When processing 32-bit data, a 16-bit architecture will take at least two instructions to perform the same task as a single ARM instruction. However, not all the code in a program will process 32-bit data (for example, code that performs character string handling), and some instructions, like Branch instructions, do not process any data at all.

If a 16-bit architecture only has 16-bit instructions, and a 32-bit architecture only has 32-bit instructions, then overall the 16-bit architecture will have better code density and better than one half the performance of the 32-bit architecture. Clearly 32-bit performance comes at the cost of code density.

THUMB breaks this constraint by implementing a 16-bit instruction length on a 32-bit architecture, making the processing of 32-bit data efficient with a compact instruction coding. This provides far better performance than a 16-bit architecture, with better code density than a 32-bit architecture. THUMB also has a major advantage over other 32-bit architectures with 16-bit instructions. This is the ability to switch back to full ARM code and execute at full speed. This enables critical loops for applications such as fast interrupts and DSP algorithms to be coded using the full ARM instruction set and linked with THUMB code. The overhead of switching from THUMB code to ARM code is folded into subroutine entry time. Various portions of a system can be optimized for speed or for code density by switching between THUMB and ARM execution as appropriate.

## **Instruction Set Summary**

The CW001007 has two instruction sets-a standard 32-bit ARM set, and a 16-bit THUMB set. Table 1 summarizes the ARM instruction set, and Table 2 summarizes the THUMB set.

| Table 1 A | <b>RM</b> Instruction | Set (32-bit) |

|-----------|-----------------------|--------------|

|-----------|-----------------------|--------------|

#### \_ . . ..

#### Table 2 Thumb Instruction Set (16-bit)

| Ор         | Description                                                      | Ор        | Description                                    |

|------------|------------------------------------------------------------------|-----------|------------------------------------------------|

|            | Instructions                                                     | Branch I  | nstructions                                    |

| В          | Branch                                                           | в         | Branch                                         |

| BL         | Branch with Link                                                 | BL        | Branch with Link                               |

| BX         | Branch and Exchange                                              | BX        | Branch and Exchange                            |

|            | ocessing Instructions                                            |           | •                                              |

| ADC        | Add with Carry                                                   |           | cessing Instructions                           |

| ADD        | Add                                                              | ADC       | Add with Carry                                 |

| AND        | Logical AND                                                      | ADD       | Add                                            |

| BIC<br>CMN | Bit Clear                                                        | AND       | Logical AND                                    |

| CMP        | Compare Negated                                                  | ASR       | Arithmetic Shift Right                         |

| EOR        | Compare<br>Logical Exclusive OR                                  | BIC       | Bit Clear                                      |

| MOV        | Move                                                             | CMN       | Compare Negative                               |

| MVN        | Move Not                                                         | CMP       | Compare                                        |

| ORR        | Logical (Inclusive) OR                                           | EOR       | Exclusive OR                                   |

| RSB        | Reverse Subtract                                                 | LSL       |                                                |

| RSC        | Reverse Subtract with Carry                                      |           | Logical Shift Left                             |

| SBC        | Subtract with Carry                                              | LSR       | Logical Shift Right                            |

| SUB        | Subtract                                                         | MOV       | Move                                           |

| TEQ        | Test Equivalence                                                 | MVN       | Move NOT                                       |

| TST        | Test                                                             | NEG       | Negate                                         |

| Multiply   | Instructions                                                     | ORR       | Logical OR                                     |

| MLA        | Multiply Accumulate                                              | ROR       | Rotate Right                                   |

| MUL        | Multiply                                                         | SBC       | Subtract with Carry                            |

| MLAL       | Multiply Accumulate Long                                         | SUB       | Subtract                                       |

| MULL       | Multiply Long                                                    | TST       | Test Bits                                      |

| -          | n Status Register (PSR) Transfer Instructions                    |           |                                                |

| MRS        | Move PSR Status/Flags to Register                                |           | nstructions                                    |

| MSR        | Move register to PSR Status/Flags                                | MUL       | Multiply                                       |

|            | d Store Instructions                                             | Load and  | d Store Instructions                           |

| LDx        | Load Multiple Registers, Byte, Word, Halfword                    | LDx       | Load Multiple Registers, Byte, Word, Halfword  |

| STx        | Store Multiple Registers, Byte, Word, Halfword                   | POP       | Pop Registers                                  |

| SWPx       | ore Instructions                                                 | PUSH      | Push Registers                                 |

|            | Swap Word/Byte Between Register and Memory<br>essor Instructions | STx       | Store Multiple Registers, Byte, Word, Halfword |

| CDP        | Coprocessor Data Processing                                      | Interrupt | Instructions                                   |

| LDC        | Load Coprocessor from Memory                                     | SWI       | Software Interrupt                             |

| MCR        | Move to Coprocessor Register from ARM                            |           |                                                |

| MRC        | Move to ARM Register from Coprocessor                            |           |                                                |

| STC        | Store Coprocessor Register to Memory                             |           |                                                |

|            | t Instructions                                                   |           |                                                |

| SWI        | Software Interrupt                                               |           |                                                |

## Differences from CW001004

This implementation of the ARM7TDMI differs from the previous LSI Logic implementation (CW001004) in the way in which the JTAG IDCODE register is implemented.

In the CW001004, the JTAG IDCODE register returned a 32-bit device identification code in a format defined by ARM Ltd. In CW001007, the register returns a value of 0 (indicating "No valid ID present"). It is possible to use the JTAG state signals that are outputs from the CW001007 to implement an IDCODE register external to the CW001007 core.

### **Signal Descriptions**

The CW001007 signals are shown in Figure 4, and are listed by functional group:

- Clocks

- Interrupts

- Bus Controls

- Debug

- Scan Test

- Boundary Scan

- Boundary Scan Control

- Processor Interface

- Memory Interface

- Memory Management Interface

- Coprocessor Interface

In the descriptions that follow, the verb *assert* means to drive TRUE or active. The verb *deassert* means to drive FALSE or inactive.

#### Figure 4 ARM7TDMI Logic Diagram

Clocks

|                     | MCLK   | Memory Clock InputInputThis clock controls the timing of all CW001007 memoryaccesses and internal operations.                                                                 |

|---------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | nWAIT  | Not WaitInputDeasserting this signal makes the core wait for an integernumber of MCLK cycles.                                                                                 |

|                     | ECLK   | External Clock OutputOutputIn normal operation, this is MCLK exported from the core.When the core is being debugged, this is DCLK.                                            |

| Interrupts          |        |                                                                                                                                                                               |

|                     | nFIQ   | Not Fast Interrupt RequestInputAn interrupt request that causes the processor to beinterrupted if taken LOW.                                                                  |

|                     | nIRQ   | Not Interrupt RequestInputThis is the same as nFIQ, but with lower priority.                                                                                                  |

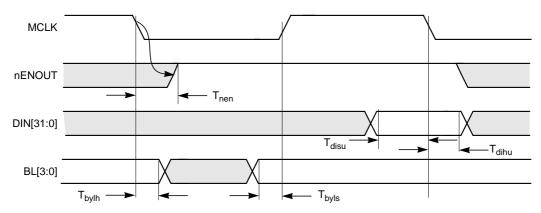

|                     | ISYNC  | Synchronous InterruptsInputWhen LOW, this signal indicates that interrupt requestinputs are to be synchronized by the ARM core.                                               |

| <b>Bus Controls</b> |        |                                                                                                                                                                               |

|                     | nRESET | Not ResetInputA LOW level causes the instruction being executed to<br>terminate abnormally. When HIGH for at least one clock<br>cycle, the processor restarts from address 0. |

|                     | BUSEN  | Data Bus ConfigurationInputDetermines whether the bidirectional data bus or the<br>unidirectional data buses are to be used.                                                  |

|                     | HIGHZ  | High Z InstructionOutputThis signal denotes that the HIGHZ instruction has beenloaded into the TAP controller.                                                                |

|                     | BIGEND | Big Endian ConfigurationInputWhen this signal is HIGH the processor treats bytes in<br>memory as being in Big Endian format.                                                  |

| nENIN   | NOT Enable Input Input<br>Used with nENOUT to control the data bus during write<br>cycles.                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

| nENOUT  | Not Enable OutputOutputDuring a data write cycle, this signal is driven LOWduring phase 1, and remains LOW for the entire cycle.   |

| nENOUTI | Not Enable OutputOutputUsed to aid arbitration in shared bus systems.                                                              |

| ABE     | Address Bus EnableInputWhen LOW, puts the address bus drivers into a highimpedance state.                                          |

| APE     | Address Pipeline EnableInputWhen HIGH, this signal enables the address timing<br>pipeline.Input                                    |

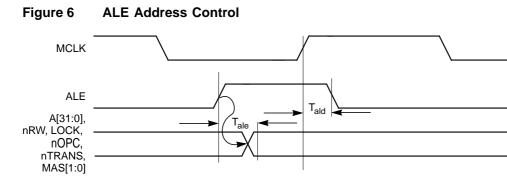

| ALE     | Address Latch EnableInputUsed to control transparent latches on the addressoutputs.                                                |

| DBE     | Data Bus EnableInputWhen driven LOW, puts the data bus into the high<br>impedance state.                                           |

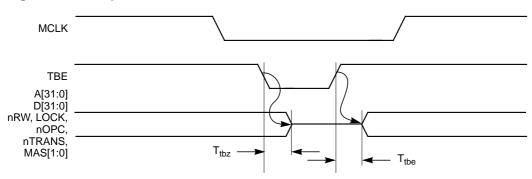

| TBE     | Test Bus EnableInputWhen LOW, puts the data bus, the address bus, LOCK,MAS[1:0], nRW, nTRANS, and nOPC into a highimpedance state. |

| BUSDIS  | Bus DisableOutputUsed to disable external logic driving onto the<br>bidirectional data bus during scan testing.                    |

| ECAPCLK | Extest Capture Clock Output<br>Removes the need for external logic to enable the<br>internal 3-state bus during scan testing.      |

| DBGRQ   | Debug RequestInputWhen HIGH causes the core to enter debug state after<br>executing the current instruction.                       |

Debug

- BREAKPT Breakpoint Input When HIGH, causes the current memory access to be breakpointed. DBGACK Debug Acknowledge Output When HIGH, indicates that the core is in debug state. **nEXEC** Not Executed Output When HIGH, indicates that the instruction in the execution unit is not being executed. EXTERN0 **External Input 0** Input Input to ICEBreaker logic that allows breakpoints and/or watchpoints to be dependent on an external condition. FXTFRN1 External Input 1 Input Input to ICEBreaker logic that allows breakpoints and/or watchpoints to be dependent on an external condition. DBGEN **Debug Enable** Input Disables the debug features of the core. **RANGEOUT0** ICEbreaker Rangeout 0 Output Indicates that the ICEBreaker watchpoint register 0 has matched the conditions currently present on the address, data and control buses. **RANGEOUT1** ICEbreaker Rangeout 1 Output This signal is the same as RANGEOUT0 but corresponds to the ICEBreaker watchpoint register 1. DBGRQI Internal Debug Request Output Represents the debug request signal that is presented to the processor. COMMRX **Communications Channel Receive** Output When HIGH, denotes that the communications channel receive buffer is empty. COMMTX Communications Channel Transmit Output When HIGH, denotes that the communications channel transmit buffer is empty. FULLSCAN Master Scan Mode Select Input

- Enables full scan input.

Scan Test

|               | RAMTEST    | Ramtest Scan Mode Select<br>Places the core in Ramtest Mode, if FULLSCAN<br>asserted.                                           | <b>Input</b><br>is       |

|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|               | RAMTEST_IN | Ramtest Scan Chain Input<br>Scan input for the core memory scan chain in R                                                      | <b>Input</b><br>amtest.  |

|               | RAMTEST_O  | UT<br>Ramtest Scan Chain Output<br>Scan output for the core memory scan chain in F<br>mode.                                     | <b>Output</b><br>Ramtest |

|               | SCAN_EN    | <b>Global Scan Enable</b><br>Enables serial loading of the scan registers throus scan chain in Production Test or Ramtest mode. | <b>Input</b><br>ugh the  |

|               | SCAN_IN    | <b>Full Scan Chain Input</b><br>Scan input for core memory scan chain in Produ<br>Test mode.                                    | <b>Input</b><br>iction   |

|               | SCAN_OUT   | <b>Full Scan Chain Output</b><br>Scan output for the core memory scan chain in<br>Production Test mode.                         | Output                   |

|               | WENCTEST   | Ramtest write enable<br>Controls core memory writes in Ramtest mode.                                                            | Input                    |

| Boundary Scan |            |                                                                                                                                 |                          |

|               | тск        | <b>Test Clock</b><br>The clock used for test operations.                                                                        | Input                    |

|               | TCK1       | <b>TCK, Phase 1</b><br>This clock represents phase 1 of TCK.                                                                    | Output                   |

|               | TCK2       | <b>TCK, Phase 2</b><br>This clock represents phase 2 of TCK.                                                                    | Output                   |

|               | TMS        | Test Mode Select<br>Selects the test mode.                                                                                      | Input                    |

|               | TDI        | <b>Test Data Input</b><br>This signal is for test data input.                                                                   | Input                    |

Output

- nTRSTNot Test ResetInputActive LOW reset signal for the boundary scan logic.

- TAPSM[3:0]

TAP Controller State Machine

Output

Shows the current state of the TAP controller state machine.

Machine

Output

- IR[3:0]

TAP Controller Instruction Register

Output

Shows the current instruction loaded into the TAP controller instruction register.

Output

- nTDOENNot TDO EnableOutputWhen LOW, this signal denotes that serial data is being<br/>driven out on the TDO output.

- SCREG[3:0] Scan Chain Register Output Shows the ID number of the scan chain currently selected by the TAP controller.

#### **Boundary Scan Control**

- DRIVEBS Boundary Scan Cell Enable Output Controls the multiplexers in the scan cells of an external boundary scan chain.

- **ECAPCLKBS** Extest Capture Clock for Boundary Scan Output Clock used to capture the core outputs during EXTEST.

- ICAPCLKB SIntest Capture Clock Output Clock used to capture the core outputs during INTEST.

- nHIGHZ Not HIGHZ Output Places the scan cells of a scan chain in the high impedance state.

- PCLKBS Boundary Scan Update Clock Output Used by an external boundary scan chain as the update clock.

- **RSTCLKBS** Boundary Scan Reset Clock Output Denotes that either the TAP controller state machine is in the RESET state or that nTRST has been asserted.

- SDINBSBoundary Scan Serial Input DataOutputThe serial data to be applied to an external scan chain.

|                    | SDOUTBS    | Boundary Scan Serial Output Data<br>The serial data out of the boundary scan chain.                                                                                     | Input                    |

|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                    | SHCLKBS    | Boundary Scan Shift Clock, Phase 1<br>Used to clock the master element of the scan cel                                                                                  | <b>Output</b><br>ls.     |

|                    | SHCLK2BS   | Boundary Scan Shift Clock, Phase 2<br>Used to clock the slave element of the scan cells.                                                                                | Output                   |

| Processor Interfac | ce         |                                                                                                                                                                         |                          |

|                    | nM[4:0]    | Not Processor Mode<br>Output signals that are the inverse of the internal<br>bits indicating the processor operation mode.                                              | <b>Output</b><br>status  |

|                    | ТВІТ       | Thumb Instruction Set Enable<br>When HIGH, denotes that the processor is executi<br>THUMB instruction set. When LOW, the processo<br>executing the ARM instruction set. | -                        |

| Memory Interface   |            |                                                                                                                                                                         |                          |

|                    | A[31:0]    | Addresses<br>This is the processor address bus.                                                                                                                         | Output                   |

|                    | D[31:0]    | Data BusBidireBidirectional bus for data transfers between the pro<br>and external memory.                                                                              | <b>ctional</b><br>cessor |

|                    | DOUT[31:0] | Data Output Bus<br>This is the data out bus, used to transfer data from<br>processor to the memory system.                                                              | Output<br>m the          |

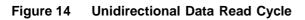

|                    | DIN[31:0]  | <b>Data Input Bus</b><br>The input data bus used to transfer instructions an<br>between the processor and memory.                                                       | <b>Input</b><br>d data   |

|                    | nMREQ      | Not Memory Request<br>When LOW, this signal indicates that the process<br>requires memory access during the following cycle                                             |                          |

|                    | SEQ        | Sequential Address<br>Becomes HIGH when the address of the next me<br>cycle is related to that of the last memory access                                                |                          |

| nRW            | Not Read/Write<br>When HIGH, indicates a processor write cycle; w<br>LOW, a read cycle.                                        | Output<br>vhen           |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| MAS[1:0]       | <b>Memory Access Size</b><br>Indicates to the external memory system whether<br>halfword, or byte length transfer is required. | <b>Output</b><br>a word, |

| BL[3:0]        | Byte Latch Control<br>These signals control when data and instructions<br>latched from the external data bus.                  | <b>Input</b><br>s are    |

| LOCK           | Locked Operation<br>When LOCK is HIGH, the processor is performin<br>"locked" memory access.                                   | Output<br>ng a           |

| mont Interface |                                                                                                                                |                          |

### Memory Management Interface

|                   | nTRANS | Not Memory Translate Output<br>When this signal is LOW it indicates that the processor is<br>in user mode.                                                                                   |

|-------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | ABORT  | Memory AbortInputAllows the memory system to tell the processor that a<br>requested access is not allowed.                                                                                   |

|                   | nOPC   | Not Op-code Fetch Output<br>When LOW, indicates that the processor is fetching an<br>instruction from memory.                                                                                |

| Coprocessor Inter | face   |                                                                                                                                                                                              |

|                   | nCPI   | Not Coprocessor InstructionOutputThis output is taken LOW when the core starts to execute<br>a coprocessor instruction.                                                                      |

|                   | CPA    | Coprocessor AbsentInputA coprocessor that is capable of performing the operationthat CW001007 is requesting should take CPA LOWimmediately.                                                  |

|                   | СРВ    | Coprocessor Busy Input<br>A coprocessor that is capable of performing the<br>requested operation, but cannot commit to starting it<br>immediately, should indicate this by driving CPB HIGH. |

## **Specifications**

This section specifies the CW001007 architecture's electrical and mechanical characteristics. The timing parameters given here are preliminary data and subject to change.

### **AC** Timing

Output load is 0.24 pF.

In the two tables that follow the letters after the signal name refer to: rising edge (r) and falling edge (f).

Values are given for two operating conditions in worst-case process:

- Table 3: Tj = 125 °C, 2.5 V 5%

- Table 4: Tj = 125 °C, 1.8 V 5%

#### Table 3 AC Parameters - Tj = 125 °C, 2.5 V

| Symbol            | Parameter                    | Min  | Max |

|-------------------|------------------------------|------|-----|

| T <sub>mck</sub>  | MCLK Cycle Time              | 12.8 |     |

| T <sub>mckl</sub> | MCLK LOW Time                | 2.8  |     |

| T <sub>mckh</sub> | MCLK HIGH Time               | 4.7  |     |

| T <sub>ws</sub>   | nWAIT Setup to MCLKr         | 2.1  |     |

| T <sub>wh</sub>   | nWAIT Hold from CKf          | 1.3  |     |

| T <sub>ale</sub>  | Address Latch Open           |      | 2.4 |

| T <sub>aleh</sub> | Address Latch Hold Time      | 1.5  |     |

| T <sub>ald</sub>  | Address Latch Time           |      | 1.5 |

| T <sub>addr</sub> | MCLKr to Address Valid       |      | 5.8 |

| T <sub>ah</sub>   | Address Hold Time from Mclkr | 3.8  |     |

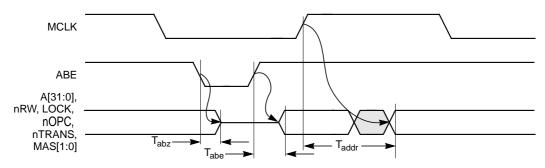

| T <sub>abe</sub>  | Address Bus Enable Time      |      | 2.5 |

| T <sub>abz</sub>  | Address Bus Disable Time     |      | 2.5 |

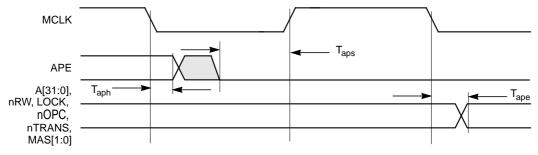

| T <sub>aph</sub>  | APE Hold Time from MCLKr     | 1.3  |     |

| Symbol             | Parameter                                   | Min | Max  |

|--------------------|---------------------------------------------|-----|------|

| T <sub>aps</sub>   | APE Setup Time to MCLKf                     | 2.8 |      |

| T <sub>ape</sub>   | MCLKf to Address Valid                      |     | 3.9  |

| T <sub>apeh</sub>  | Address Group Hold Time from MCLKf          | 3.1 |      |

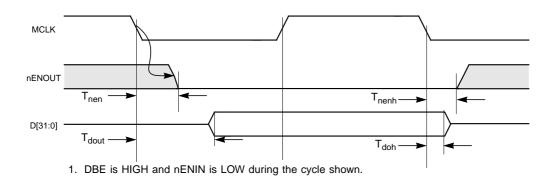

| T <sub>dout</sub>  | MCLKf to D[31:0] Valid                      |     | 7.6  |

| T <sub>doh</sub>   | D[31:0] Out Hold from MCLKf                 | 0.9 |      |

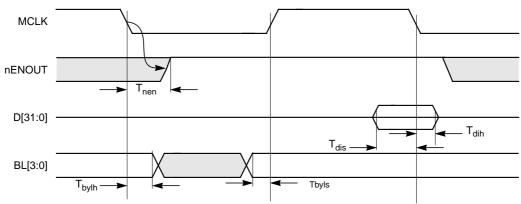

| T <sub>dis</sub>   | D[31:0] In Setup Time to MCLKf              | 1.7 |      |

| T <sub>dih</sub>   | D[31:0] In Hold Time from MCLKf             | 1.7 |      |

| T <sub>doutu</sub> | MCLKf to DOUT[31:0] Valid                   |     | 8.1  |

| T <sub>dohu</sub>  | DOUT[31:0] Hold Time from MCLKf             | 5.0 |      |

| T <sub>disu</sub>  | DIN[31:0] Setup Time to MCLKf               | 2.0 |      |

| T <sub>dihu</sub>  | DIN Hold Time to MCLKf                      | 2.0 |      |

| T <sub>nen</sub>   | MCLKf to nENOUT Valid                       |     | 4.1  |

| T <sub>nenh</sub>  | nENOUT Hold Time from MCLKf                 | 3.6 |      |

| T <sub>bylh</sub>  | BL[3:0] Hold Time from MCLKf                | 1.3 |      |

| T <sub>byls</sub>  | BL[3:0] Setup to from MCLKr                 | 0   |      |

| T <sub>dbe</sub>   | Data Bus Enable Time from DBEr              |     | 5.1  |

| T <sub>dbz</sub>   | Data Bus Disable Time from DBEf             |     | 5.1  |

| T <sub>dbnen</sub> | DBE to nENOUT Valid                         |     | 1.3  |

| T <sub>tbz</sub>   | Address and Data Bus Disable Time from TBEf |     | 2.7  |

| T <sub>tbe</sub>   | Address and Data Bus Enable Time from TBEr  |     | 2.7  |

| T <sub>rwd</sub>   | MCLKr to nRW Valid                          |     | 4.7  |

| T <sub>rwh</sub>   | nRW Hold Time from MCLKr                    | 4.0 |      |

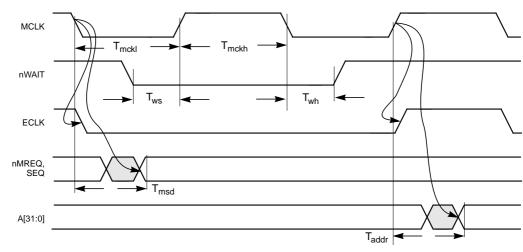

| T <sub>msd</sub>   | MCLKf to nMREQ & SEQ Valid                  |     | 10.6 |

| T <sub>msh</sub>   | nMREQ and SEQ Hold Time from MCLKf          | 3.4 |      |

| T <sub>bld</sub>   | MCLKr to MAS[1:0] and LOCK                  |     | 7.0  |

### Table 3 AC Parameters - $Tj = 125 \circ C$ , 2.5 V (Cont.)

| Symbol            | Parameter                                                                         | Min | Max |

|-------------------|-----------------------------------------------------------------------------------|-----|-----|

| T <sub>blh</sub>  | MAS[1:0] and LOCK Hold from MCLKr                                                 | 4.0 |     |

| T <sub>mdd</sub>  | MCLKr to nTRANS, nM[4:0], and TBIT Valid                                          |     | 5.8 |

| T <sub>mdh</sub>  | nTRANS and nM[4:0] Hold Time from MCLKr                                           | 3.6 |     |

| T <sub>opcd</sub> | MCLKr to nOPC Valid                                                               |     | 6.2 |

| T <sub>opch</sub> | nOPC Hold Time from MCLKr                                                         | 4.1 |     |

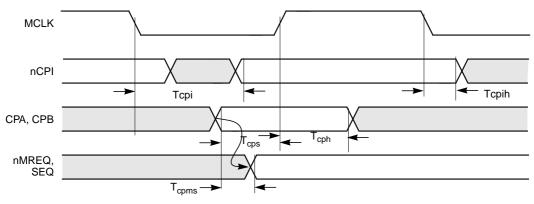

| T <sub>cps</sub>  | CPA, CPB Setup to MCLKr                                                           | 0   |     |

| T <sub>cph</sub>  | CPA,CPB Hold Time from MCLKr                                                      | 1.6 |     |

| T <sub>cpms</sub> | CPA, CPB to nMREQ, SEQ                                                            |     | 6.9 |

| T <sub>cpi</sub>  | MCLKf to nCPI Valid                                                               |     | 6.1 |

| T <sub>cpih</sub> | nCPI Hold Time from MCLKf                                                         | 3.4 |     |

| T <sub>cts</sub>  | Config Setup Time                                                                 | 0   |     |

| T <sub>cth</sub>  | Config Hold Time                                                                  | 1.5 |     |

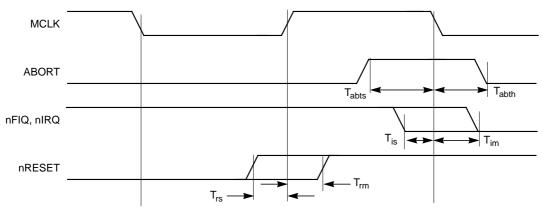

| T <sub>abts</sub> | ABORT Setup Time to MCLKf                                                         | 1.2 |     |

| T <sub>abth</sub> | ABORT Hold Time from MCLKf                                                        | 1.2 |     |

| T <sub>is</sub>   | Asynchronous Interrupt Setup Time to MCLKf for Guaranteed Recognition (ISYNC = 0) | 0.1 |     |

| T <sub>im</sub>   | Asynchronous Interrupt Guaranteed Nonrecognition Time<br>(ISYNC = 0)              |     | 1.4 |

| T <sub>sis</sub>  | Synchronous nFIQ, nIRQ Setup to MCLKf (ISYNC = 1)                                 | 0.1 |     |

| T <sub>sih</sub>  | Synchronous nFIQ, nIRQ Hold from MCLKf (ISYNC = 1)                                | 1.4 |     |

| T <sub>rs</sub>   | Reset Setup Time to MCLKr for Guaranteed Recognition                              | 0   |     |

| T <sub>rm</sub>   | Reset Guaranteed Nonrecognition Time                                              | 0.8 |     |

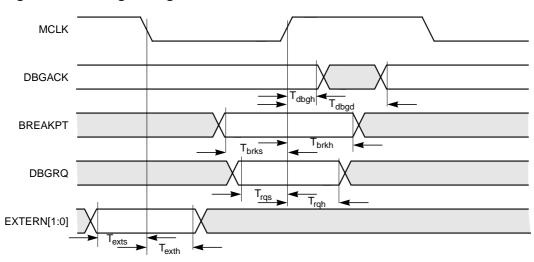

| T <sub>exd</sub>  | MCLKf to nEXEC Valid                                                              |     | 6.3 |

| T <sub>exh</sub>  | nEXEC Hold Time from MCLKf                                                        | 3.7 |     |

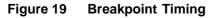

| T <sub>brks</sub> | Setup Time of BREAKPT to MCLKr                                                    | 0   |     |

| T <sub>brkh</sub> | Hold Time of BREAKPT from MCLKr                                                   |     | 1.7 |

### Table 3 AC Parameters - $Tj = 125 \circ C$ , 2.5 V (Cont.)

| Symbol             | Parameter                                                     | Min           | Max |

|--------------------|---------------------------------------------------------------|---------------|-----|

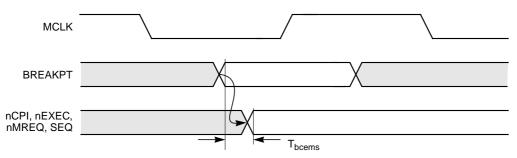

| T <sub>bcems</sub> | BREAKPT to nCPI, nEXEC, nMREQ, SEQ Delay                      |               | 7.1 |

| T <sub>dbgd</sub>  | MCLKr to DBGACK Valid                                         |               | 8.2 |

| T <sub>dbgh</sub>  | DGBACK Hold Time from MCLKr                                   | 3.7           |     |

| T <sub>rqs</sub>   | DBGRQ Setup Time to MCLKr for Guaranteed Recognition          | 1.1           |     |

| T <sub>rqh</sub>   | DBGRQ Guaranteed Nonrecognition time                          | 0             |     |

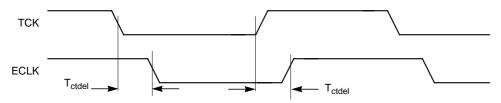

| T <sub>cdel</sub>  | MCLK to ECLK Delay                                            |               | 0.7 |

| T <sub>ctdel</sub> | TCK to ECLK Delay                                             |               | 1.0 |

| T <sub>exts</sub>  | EXTERN[1:0] Setup Time to MCLKf                               | 0             |     |

| T <sub>exth</sub>  | EXTERN[1:0] Hold Time from MCLKf                              | 1.2           |     |

| T <sub>rg</sub>    | MCLKf to RANGEOUT0, RANGEOUT1 Valid                           |               | 4.8 |

| T <sub>rgh</sub>   | RANGEOUT0, RANGEOUT1 Hold Time from MCLKf                     | 3.1           |     |

| T <sub>dbgrq</sub> | DBGRQ to DBGRQI Valid                                         |               | 1.1 |

| T <sub>rstd</sub>  | nRESETf to D[], DBGACK, nCPI, nENOUT, nEXEC, nMREQ, SEQ Valid |               | 6.2 |

| T <sub>commd</sub> | MCLKr to COMMRX, COMMTX Valid                                 |               | 1.9 |

| T <sub>trstd</sub> | nTRSTf to Every Output Valid                                  |               | 7.6 |

| T <sub>rstl</sub>  | nRESET LOW for Guaranteed Reset                               | 2 MCLK cycles |     |

### Table 3 AC Parameters - $Tj = 125 \circ C$ , 2.5 V (Cont.)

| Symbol             | Parameter                          | Min  | Max  |

|--------------------|------------------------------------|------|------|

| T <sub>mck</sub>   | MCLK Cycle Time                    | 20.8 |      |

| T <sub>mckl</sub>  | MCLK LOW Time                      | 6.9  |      |

| T <sub>mckh</sub>  | MCLK HIGH Time                     | 7.1  |      |

| T <sub>ws</sub>    | nWAIT Setup to MCLKr               | 3.0  |      |

| T <sub>wh</sub>    | nWAIT Hold from CKf                | 1.8  |      |

| T <sub>ale</sub>   | Address Latch Open                 |      | 3.4  |

| T <sub>aleh</sub>  | Address Latch Hold Time            | 2.3  |      |

| T <sub>ald</sub>   | Address Latch Time                 |      | 2.3  |

| T <sub>addr</sub>  | MCLKr to Address Valid             |      | 11.8 |

| T <sub>ah</sub>    | Address Hold Time from MCLKr       | 5.7  |      |

| T <sub>abe</sub>   | Address Bus Enable Time            |      | 3.7  |

| T <sub>abz</sub>   | Address Bus Disable Time           |      | 3.8  |

| T <sub>aph</sub>   | APE Hold Time from MCLKr           | 1.9  |      |

| T <sub>aps</sub>   | APE Setup Time to MCLKf            | 4.2  |      |

| T <sub>ape</sub>   | MCLKf to Address Valid             |      | 6.0  |

| T <sub>apeh</sub>  | Address Group Hold Time from MCLKf | 4.7  |      |

| T <sub>dout</sub>  | MCLKf to D[31:0] Valid             |      | 11.6 |

| T <sub>doh</sub>   | D[31:0] Out Hold from MCLKf        | 1.4  |      |

| T <sub>dis</sub>   | D[31:0] In Setup Time to MCLKf     | 1.8  |      |

| T <sub>dih</sub>   | D[31:0] In Hold Time from MCLKf    | 2.5  |      |

| T <sub>doutu</sub> | MCLKf to DOUT[31:0] Valid          |      | 12.1 |

| T <sub>dohu</sub>  | DOUT[31:0] Hold Time from MCLKf    | 7.5  |      |

| T <sub>disu</sub>  | DIN[31:0] Setup Time to MCLKf      | 2.7  |      |

| T <sub>dihu</sub>  | DIN[hold Time to MCLKf             | 2.9  |      |

| T <sub>nen</sub>   | MCLKf to nENOUT Valid              |      | 6.2  |

### Table 4AC Parameters - Tj = 125 °C, 1.8 V

| Symbol             | Parameter                                   | Min | Max  |

|--------------------|---------------------------------------------|-----|------|

| T <sub>nenh</sub>  | nENOUT Hold Time from MCLKf                 | 5.4 |      |

| T <sub>bylh</sub>  | BL[3:0] Hold Time from MCLKf                | 1.8 |      |

| T <sub>byls</sub>  | BL[3:0] Setup to from MCLKr                 | 0   |      |

| T <sub>dbe</sub>   | Data Bus Enable Time from DBEr              |     | 7.5  |

| T <sub>dbz</sub>   | Data Bus Disable Time from DBEf             |     | 7.4  |

| T <sub>dbnen</sub> | DBE to nENOUT Valid                         |     | 2.0  |

| T <sub>tbz</sub>   | Address and Data Bus Disable Time from TBEf |     | 3.7  |

| T <sub>tbe</sub>   | Address and Data Bus Enable Time from TBEr  |     | 3.9  |

| T <sub>rwd</sub>   | MCLKr to nRW Valid                          |     | 10.1 |

| T <sub>rwh</sub>   | nRW Hold Time from MCLKr                    | 6.1 |      |

| T <sub>msd</sub>   | MCLKf to nMREQ and SEQ Valid                |     | 16.2 |

| T <sub>msh</sub>   | nMREQ and SEQ Hold Time from MCLKf          | 5.0 |      |

| T <sub>bld</sub>   | MCLKr to MAS[1:0] and LOCK                  |     | 12.6 |

| T <sub>blh</sub>   | MAS[1:0] and LOCK Hold from MCLKr           | 5.9 |      |

| T <sub>mdd</sub>   | MCLKr to nTRANS, nM[4:0], and TBIT Valid    |     | 11.8 |

| T <sub>mdh</sub>   | nTRANS and nM[4:0] Hold Time from MCLKr     | 5.3 |      |

| T <sub>opcd</sub>  | MCLKr to nOPC Valid                         |     | 12.5 |

| T <sub>opch</sub>  | nOPC Hold Time from MCLKr                   | 6.3 |      |

| T <sub>cps</sub>   | CPA, CPB Setup to MCLKr                     | 0   |      |

| T <sub>cph</sub>   | CPA,CPB Hold Time from MCLKr                | 2.2 |      |

| T <sub>cpms</sub>  | CPA, CPB to nMREQ, SEQ                      |     | 10.5 |

| T <sub>cpi</sub>   | MCLKf to nCPI Valid                         |     | 9.3  |

| T <sub>cpih</sub>  | nCPI Hold Time from MCLKf                   | 5.1 |      |

| T <sub>cts</sub>   | Config Setup Time                           | 0   |      |

| T <sub>cth</sub>   | Config Hold Time                            | 2.1 |      |

### Table 4AC Parameters - Tj = 125 °C, 1.8 V (Cont.)

| Symbol             | ol Parameter                                                                      |     | Max  |  |

|--------------------|-----------------------------------------------------------------------------------|-----|------|--|

| T <sub>abts</sub>  | ABORT Setup Time to MCLKf                                                         | 1.8 |      |  |

| T <sub>abth</sub>  | ABORT Hold Time from MCLKf                                                        | 1.7 |      |  |

| T <sub>is</sub>    | Asynchronous Interrupt Setup Time to MCLKf for Guaranteed Recognition (ISYNC = 0) | 0.3 |      |  |

| T <sub>im</sub>    | Asynchronous Interrupt Guaranteed Nonrecognition Time<br>(ISYNC = 0)              |     | 2.0  |  |

| T <sub>sis</sub>   | Synchronous nFIQ, nIRQ Setup to MCLKf (ISYNC = 1)                                 | 0.3 |      |  |

| T <sub>sih</sub>   | Synchronous nFIQ, nIRQ Hold from MCLKf (ISYNC = 1)                                | 2.0 |      |  |

| T <sub>rs</sub>    | Reset Setup Time to MCLKr for Guaranteed Recognition                              | 0   |      |  |

| T <sub>rm</sub>    | Reset Guaranteed Nonrecognition Time                                              | 1.2 |      |  |

| T <sub>exd</sub>   | MCLKf to nEXEC Valid                                                              |     | 9.6  |  |

| T <sub>exh</sub>   | nEXEC Hold Time from MCLKf                                                        | 5.4 |      |  |

| T <sub>brks</sub>  | Setup Time of BREAKPT to MCLKr                                                    | 0   |      |  |

| T <sub>brkh</sub>  | Hold Time of BREAKPT from MCLKr                                                   |     | 2.5  |  |

| T <sub>bcems</sub> | BREAKPT to nCPI, nEXEC, nMREQ, SEQ Delay                                          |     | 10.7 |  |

| T <sub>dbgd</sub>  | MCLKr to DBGACK Valid                                                             |     | 12.0 |  |

| T <sub>dbgh</sub>  | DGBACK Hold Time from MCLKr                                                       | 5.5 |      |  |

| T <sub>rqs</sub>   | DBGRQ Setup Time to MCLKr for Guaranteed Recognition                              | 1.7 |      |  |

| T <sub>rqh</sub>   | DBGRQ Guaranteed Nonrecognition Time                                              | 0   |      |  |

| T <sub>cdel</sub>  | MCLK to ECLK Delay                                                                |     | 1.1  |  |

| T <sub>ctdel</sub> | TCK to ECLK Delay                                                                 |     | 1.5  |  |

| T <sub>exts</sub>  | EXTERN[1:0] Setup Time to MCLKf                                                   | 0   |      |  |

| T <sub>exth</sub>  | EXTERN[1:0] Hold Time from MCLKf                                                  | 1.7 |      |  |

| T <sub>rg</sub>    | MCLKf to RANGEOUT0, RANGEOUT1 Valid                                               |     | 7.4  |  |

### Table 4AC Parameters - Tj = 125 °C, 1.8 V (Cont.)

### Table 4AC Parameters - Tj = 125 °C, 1.8 V (Cont.)

| Symbol             | Parameter                                                     | Min           | Max  |

|--------------------|---------------------------------------------------------------|---------------|------|

| T <sub>rgh</sub>   | RANGEOUT0, RANGEOUT1 Hold Time from MCLKf                     | 4.6           |      |

| T <sub>dbgrq</sub> | DBGRQ to DBGRQI Valid                                         |               | 1.7  |

| T <sub>rstd</sub>  | nRESETf to D[], DBGACK, nCPI, nENOUT, nEXEC, nMREQ, SEQ Valid |               | 8.1  |

| T <sub>commd</sub> | MCLKr to COMMRX, COMMTX Valid                                 |               | 2.9  |

| T <sub>trstd</sub> | nTRSTf to Every Output Valid                                  |               | 13.6 |

| T <sub>rstl</sub>  | nRESET LOW for Guaranteed Reset                               | 2 MCLK cycles |      |

### **Timing Diagrams**

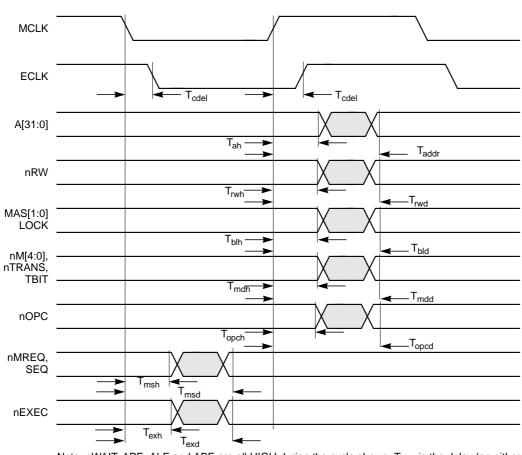

#### Figure 5 General Timing

Note: nWAIT, APE, ALE and ABE are all HIGH during the cycle shown.  $T_{odel}$  is the delay (on either edge) from MCLK changing to ECLK changing.

- 1.  $\mathrm{T}_{\mathrm{ald}}$  is the time by which ALE must be driven LOW in order to latch the current address in phase

- 2. If ALE is driven low after  $T_{ald},$  then a new address will be latched.

Figure 7 APE Address Control

Figure 8 ABE Address Control (APE high)

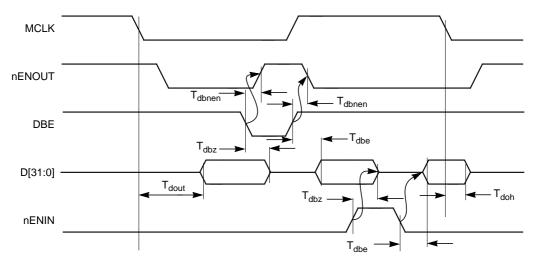

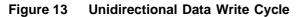

#### Figure 10 Bidirectional Data Read Cycle

**Bidirectional Data Write Cycle**

Figure 9

1. DBE is HIGH and nENIN is LOW during the cycle shown.

Figure 11 Data Bus Control

1. The cycle shown is a data write cycle since nENOUT was driven LOW during phase.

2. Here, DBE has first been used to modify the behavior of the data bus, and then nENIN.

Figure 16 Coprocessor Timing

Normally, nMREQ and SEQ become valid T<sub>msd</sub> after the falling edge of MCLK. In this cycle the ARM has been busy-waiting, waiting for a coprocessor to complete the instruction. If CPA and CPB change during phase 1, the timing of nMREQ and SEQ will depend on T<sub>cpms</sub>. Most systems should be able to generate CPA and CPB during the previous phase 2, and so the timing of nMREQ and SEQ will always be T<sub>msd</sub>.

#### Figure 17 Exception Timing

T<sub>is</sub>/T<sub>rs</sub> guarantee recognition of the interrupt (or reset) source by the corresponding clock edge. T<sub>im</sub>/T<sub>rm</sub> guarantee nonrecognition by that clock edge. These inputs may be applied fully asynchronously where the exact cycle of recognition is unimportant.

#### Figure 18 Debug Timing

1. BREAKPT changing in the LOW phase of MCLK to signal a watchpointed store can affect nCPI, nEXEC, nMREQ, and SEQ in the LOW phase of MCLK.

The ARM7TDMI core is not clocked by the HIGH phase of MCLK enveloped by nWAIT. Thus, during the cycles shown, nMREQ and SEQ change once, during the first LOW phase of MCLK, and A[31:0] change once, during the second HIGH phase of MCLK.

#### **Absolute Maximum Ratings**

**MCLK** Timing

Figure 21

Table 5 lists the absolute maximum ratings for the G11 technology. Exceeding these values may permanently damage the device. Operating the device at absolute maximum ratings for extended periods may affect device reliability.

#### Table 5 Absolute Maximum Ratings (Referenced to VSS)

| Symbol          | Parameter                        | Min  | Мах       | Units |

|-----------------|----------------------------------|------|-----------|-------|

| V <sub>DD</sub> | Supply voltage                   | -0.3 | 3.1       | V     |

| V <sub>in</sub> | Input voltage applied to any pin | -1.0 | VDD + 0.3 | V     |

| Τ <sub>s</sub>  | Storage temperature              | -40  | 125       | °C    |

### **DC Operating Conditions**

Table 6 defines the recommended operating supply voltage and temperature for the G11-p technology.

#### Table 6 G11-p Recommended Operation Conditions

| Symbol           | Parameter                      | Min       | Тур | Мах       | Units | Notes |

|------------------|--------------------------------|-----------|-----|-----------|-------|-------|

| V <sub>DD</sub>  | Supply voltage                 | 2.25      | 2.5 | 2.75      | V     |       |

| V <sub>ihc</sub> | IC input HIGH voltage          | 2.0       |     | VDD + 0.3 | V     | 1,2   |

| V <sub>ilc</sub> | IC input LOW voltage           | VSS – 0.5 |     | 0.8       | V     | 1,2   |

| TJ               | Operating junction temperature | 0         |     | +115      | °C    |       |

- 1. Voltages measured with respect to VSS.

- 2. IC CMOS-level inputs.

Table 7 defines the recommended operating supply voltage and temperature for the G11-v technology.

#### Table 7 G11-v Recommended Operation Conditions

| Symbol           | Parameter                      | Min       | Тур | Max       | Units | Notes |

|------------------|--------------------------------|-----------|-----|-----------|-------|-------|

| V <sub>DD</sub>  | Supply voltage                 | 1.62      | 1.8 | 1.98      | V     |       |

| V <sub>ihc</sub> | IC input HIGH voltage          | 1.05      |     | VDD + 0.3 | V     | 1,2   |

| V <sub>ilc</sub> | IC input LOW voltage           | VSS - 0.5 |     | 0.7       | V     | 1,2   |

| TJ               | Operating junction temperature | 0         |     | +115      | °C    |       |

1. Voltages measured with respect to VSS.

2. IC CMOS-level inputs.

#### Sales Offices and Design Resource Centers

LSI Logic Corporation Corporate Headquarters Tel: 408.433.8000 Fax: 408.433.8989

#### NORTH AMERICA

California Irvine

Tel: 949.553.5600 Fax: 949.474.8101

Pleasanton Design Center Tel: 925.730.8800 Fax: 925.730.8700

San Diego Tel: 619.613.8300 Fax: 619.613.8350

Wireless Design Center Tel: 619.350.5560 Fax: 619.350.0171

Silicon Valley Tel: 408.433.8000 Fax: 408.954.3353

> Colorado Boulder Tel: 303.447.3800 Fax: 303.541.0641

> Florida Boca Raton Tel: 561.989.3236 Fax: 561.989.3237

> Georgia Roswell Tel: 770.641.8001 Fax: 770.641.8005

Illinois Schaumburg Tel: 847.995.1600 Fax: 847.995.1622

Kentucky Bowling Green Tel: 502.793.0010 Fax: 502.793.0040

Maryland Bethesda Tel: 301.897.5800 Fax: 301.897.8389

Massachusetts Waltham Tel: 781.890.0180 Fax: 781.890.6158

Minnesota Minneapolis Tel: 612.921.8300 Fax: 612.921.8399 New Jersey Edison

Tel: 732.549.4500

Fax: 732.549.4802

New York Fairport Tel: 716.218.0020 Fax: 716.218.9010

North Carolina Raleigh Tel: 919.785.4520 Fax: 919.783.8909

Oregon Beaverton Tel: 503.645.0589 Fax: 503.645.6612

**Texas** Austin Tel: 512.388.7294 Fax: 512.388.4171

Dallas Tel: 972.503.3205 Fax: 972.503.2258

Tel: 972.244.5000 Fax: 972.244.5001

> Houston Tel: 281.379.7800 Fax: 281.379.7818

Washington Issaquah Tel: 425.837.1733 Fax: 425.837.1734

Canada Ontario Ottawa

Tel: 613.592.1263

Fax: 613.592.3253

Toronto

Tel: 416.620.7400 Fax: 416.620.5005

Quebec Montreal

Tel: 514.694.2417 Fax: 514.694.2699

#### INTERNATIONAL

Australia New South Wales Reptechnic Pty Ltd ◆ Tel: 612.9953.9844 Fax: 612.9953.9683 China Beijing LSI Logic International Services Inc Tel: 86.10.6804.2534 Fax: 86.10.6804.2521

France Paris LSI Logic S.A. Immeuble Europa Tel: 33.1.34.63.13.13 Fax: 33.1.34.63.13.19

Germany Munich LSI Logic GmbH Tel: 49.89.4.58.33.0

Fax: 49.89.4.58.33.108 Stuttgart Tel: 49.711.13.96.90 Fax: 49.711.86.61.428

Hong Kong Hong Kong AVT Industrial Ltd Tel: 852.2428.0008 Fax: 852.2401.2105

India Bangalore Spike Technologies India Private Ltd ↑ Tel: 91.80.664.5530

Fax: 91.80.664.9748 Israel Ramat Hasharon

LSI Logic ♦ Tel: 972.3.5.480480 Fax: 972.3.5.403747

Netanya VLSI Development Centre Tel: 972.9.657190 Fax: 972.9.657194

Italy Milano LSI Logic S.P.A.

Tel: 39.039.687371

Fax: 39.039.6057867

Japan Tokyo LSI Logic K.K. ♦ Tel: 81.3.5463.7821 Fax: 81.3.5463.7820

Osaka ♦ Tel: 81.6.947.5281 Fax: 81.6.947.5287 Korea Seoul LSI Logic Corporation of Korea Ltd ◆ Tel: 82.2.528.3400

Fax: 82.2.528.3400

The Netherlands Eindhoven LSI Logic Europe Ltd Tel: 31.40.265.3580 Fax: 31.40.296.2109

Singapore Singapore LSI Logic Pte Ltd ◆ Tel: 65.334.9061

Fax: 65.334.4749 Tel: 65.835.5040

Fax: 65.732.5047 Sweden

Stockholm **LSI Logic AB** ♦ Tel: 46.8.444.15.00 Fax: 46.8.750.66.47

> Switzerland Brugg/Biel LSI Logic Sulzer AG Tel: 41.32.536363 Fax: 41.32.536367

Taiwan Taipei LSI Logic Asia-Pacific ♦ Tel: 886.2.2718.7828

Fax: 886.2.2718.8869 Avnet-Mercuries Corporation, Ltd

Tel: 886.2.2503.1111 Fax: 886.2.2503.1449

Jeilin Technology Corporation, Ltd Tel: 886.2.2248.4828 Fax: 886.2.2242.4397

Lumax International Corporation, Ltd Tel: 886.2.2788.3656 Fax: 886.2.2788.3568

Prospect Technology Corporation, Ltd Tel: 886.2.2721.9533 Fax: 886.2.2773.3756

United Kingdom Bracknell

◆ Tel: 44.1344.426544 Fax: 44.1344.481039

Sales Offices with Design Resource Centers

To receive product literature, visit us at http://www.lsilogic.com

#### **ISO 9000 Certified**

Printed in USA Order No.C15039 Doc. No. DB08-000121-00 The LSI Logic logo design and CoreWare are registered trademarks and G11 is a trademark of LSI Logic Corporation. ARM is a registered trademark of Advanced RISC Machines Limited, used under license. All other brand and product names may be trademarks of their respective companies. LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties.